半導體測試高壓電源的噪聲抑制

在半導體測試領(lǐng)域,高壓電源起著至關(guān)重要的作用。然而,噪聲問題卻常常困擾著高壓電源的應(yīng)用,對測試結(jié)果的準確性和可靠性產(chǎn)生負面影響。因此,深入研究半導體測試高壓電源的噪聲抑制具有極為重要的意義。

高壓電源產(chǎn)生噪聲的原因是多方面的。首先,內(nèi)部電子元件的特性和工作狀態(tài)是重要因素。例如,開關(guān)元件在快速切換過程中會產(chǎn)生電磁干擾,這種干擾以電磁波的形式向外傳播,成為噪聲源。其次,電源電路的布局和布線不合理也會引發(fā)噪聲。如果線路之間的距離過近或者存在環(huán)路,就容易形成電磁耦合,導致噪聲的產(chǎn)生和傳播。再者,外部環(huán)境因素如電網(wǎng)電壓的波動、周圍其他電氣設(shè)備的電磁輻射等也會對高壓電源產(chǎn)生干擾,進一步加劇噪聲問題。

噪聲對半導體測試會造成諸多不良影響。在高精度的半導體參數(shù)測試中,噪聲可能會掩蓋被測器件的真實信號,使得測試數(shù)據(jù)出現(xiàn)偏差。例如,對于一些微弱信號的檢測,噪聲可能會導致誤判,將原本正常的信號視為異常,或者反之。這對于半導體產(chǎn)品的質(zhì)量評估和性能分析是極為不利的,可能會導致次品流入市場或者對產(chǎn)品進行不必要的改進,增加生產(chǎn)成本和時間成本。

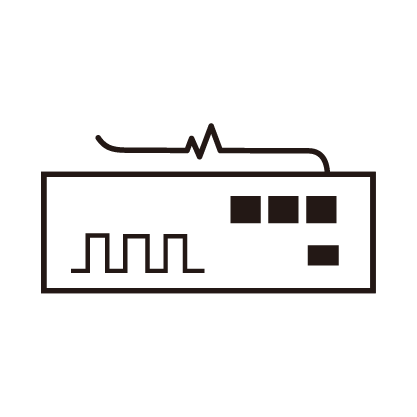

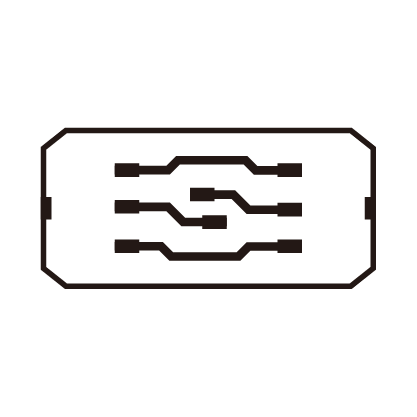

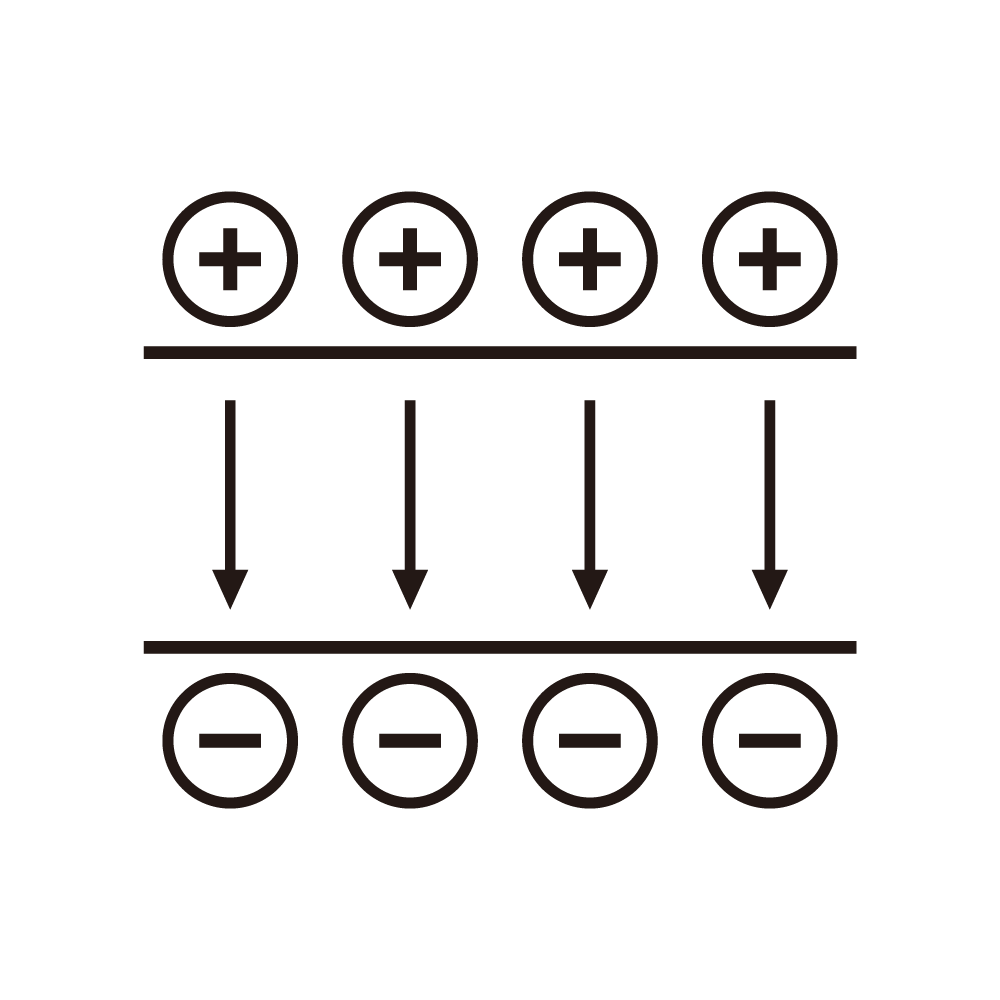

為了抑制半導體測試高壓電源的噪聲,可以從多個方面采取措施。在電源電路設(shè)計層面,采用合適的濾波電路是關(guān)鍵。例如,低通濾波器可以有效地濾除高頻噪聲,讓直流或低頻信號順利通過,從而減少噪聲對輸出電壓的影響。同時,優(yōu)化開關(guān)元件的驅(qū)動電路,使其能夠更加平穩(wěn)地切換,降低開關(guān)過程中產(chǎn)生的電磁干擾。在電路布局方面,遵循電磁兼容原則,合理安排各個元件的位置,增大線路之間的距離,減少電磁耦合。采用多層電路板設(shè)計,將不同功能的線路分層布置,并設(shè)置專門的地層和電源層,為噪聲提供良好的回流路徑,從而降低噪聲在電路板上的傳播。

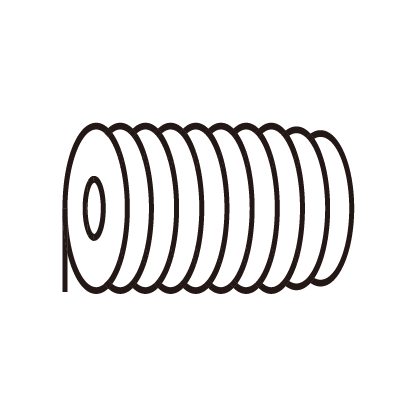

此外,屏蔽技術(shù)也是抑制噪聲的有效手段。對高壓電源的關(guān)鍵部分進行屏蔽,可以阻擋外部電磁輻射的侵入,同時也能防止內(nèi)部噪聲向外泄漏。屏蔽材料的選擇要根據(jù)具體的需求和頻率范圍來確定,如金屬屏蔽罩對于高頻電磁干擾有較好的屏蔽效果。在電源的輸入和輸出端,采用磁珠、共模電感等元件來抑制共模噪聲和差模噪聲。這些元件能夠利用其特殊的電磁特性,對噪聲電流形成阻礙,而對正常的信號電流影響較小。

在軟件控制方面,也可以通過算法來實現(xiàn)噪聲抑制。例如,采用數(shù)字信號處理技術(shù)對輸出電壓進行實時監(jiān)測和分析,當檢測到噪聲信號時,通過反饋控制調(diào)整電源的輸出,以補償噪聲對電壓的影響。這種軟件與硬件相結(jié)合的方式能夠更加全面地抑制噪聲,提高高壓電源在半導體測試中的性能。

綜上所述,半導體測試高壓電源的噪聲抑制是一個復雜而系統(tǒng)的工程,需要從電路設(shè)計、布局布線、屏蔽技術(shù)以及軟件控制等多個方面綜合考慮并采取有效的措施。只有這樣,才能最大程度地降低噪聲對測試結(jié)果的影響,提高半導體測試的準確性和可靠性,為半導體產(chǎn)業(yè)的發(fā)展提供有力的技術(shù)支持。隨著半導體技術(shù)的不斷進步,對于高壓電源噪聲抑制的要求也會越來越高,相關(guān)技術(shù)的研究和創(chuàng)新也將持續(xù)推進。