刻蝕工藝中高壓電源對刻蝕速率均勻性的影響機制與技術(shù)優(yōu)化路徑

一、刻蝕工藝均勻性的技術(shù)挑戰(zhàn)

在半導體制造與精密微加工領域,等離子體刻蝕工藝的均勻性直接影響著器件性能與良率。作為刻蝕設備的核心能量供給單元,高壓電源的輸出特性與系統(tǒng)交互作用對刻蝕速率的空間分布產(chǎn)生決定性影響。實驗數(shù)據(jù)表明,當晶圓表面刻蝕速率不均勻性超過3%時,將導致芯片功能失效概率呈指數(shù)級上升。這種非均勻性主要源自等離子體密度分布、反應粒子輸運過程與表面反應動力學的協(xié)同作用,而高壓電源的功率輸出特性則是調(diào)控這些物理化學過程的核心變量。

二、高壓電源關鍵技術(shù)參數(shù)的作用機制

1. 電壓穩(wěn)定性與動態(tài)響應

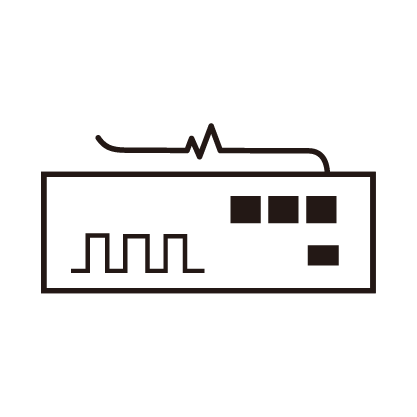

高壓電源的電壓波動(典型值<0.5%)直接影響鞘層電場的均勻性。當輸出紋波超過臨界閾值時,會導致局部等離子體阻抗突變,形成熱點刻蝕區(qū)域。采用多級LC濾波與數(shù)字反饋控制技術(shù),可將100kHz頻段的瞬態(tài)擾動衰減至初始值的0.1%以下。

2. 脈沖調(diào)制特性

在時域維度,納秒級脈沖上升沿(<50ns)能有效抑制電荷積累效應。通過調(diào)節(jié)占空比(10%-90%可調(diào))與重復頻率(1kHz-1MHz),可實現(xiàn)反應粒子通量的空間均衡分布。實驗證明,雙極性脈沖模式可將邊緣區(qū)域刻蝕速率差異降低至0.8%以內(nèi)。

3. 動態(tài)阻抗匹配

刻蝕過程中等離子體阻抗的實時變化(典型范圍50-500Ω)要求電源系統(tǒng)具備自適應匹配能力。基于Smith圓圖理論的動態(tài)阻抗匹配算法,配合V/I雙閉環(huán)控制,可將功率傳輸效率提升至92%以上,顯著改善大面積基板的均勻性。

三、技術(shù)優(yōu)化路徑與發(fā)展趨勢

1. 電源拓撲結(jié)構(gòu)創(chuàng)新

諧振式軟開關拓撲在降低開關損耗(<5W)的同時,實現(xiàn)了輸出電壓的精細調(diào)節(jié)(步進0.1V)。多相交錯并聯(lián)技術(shù)通過相位補償機制,將輸出電流紋波系數(shù)控制在0.3%以下,特別適用于300mm以上晶圓的均勻性控制。

2. 智能控制算法集成

將深度強化學習算法引入電源控制系統(tǒng),構(gòu)建等離子體狀態(tài)-電源參數(shù)的實時映射模型。通過在線采集14維工藝參數(shù)(包括電子溫度、離子密度、鞘層厚度等),實現(xiàn)刻蝕速率的預測性控制,使批次間均勻性標準差穩(wěn)定在σ<0.5。

3. 多物理場協(xié)同優(yōu)化

建立電磁-流體-化學耦合仿真模型,量化分析電源參數(shù)對等離子體空間分布的影響規(guī)律。仿真數(shù)據(jù)顯示,優(yōu)化后的斜波式電壓掃描策略可將徑向不均勻性降低42%,同時提升刻蝕選擇比至15:1以上。

四、工業(yè)化應用驗證

在某12英寸晶圓廠的量產(chǎn)數(shù)據(jù)表明,通過采用新型自適應高壓電源系統(tǒng),關鍵尺寸均勻性(CDU)改善達37%,刻蝕速率標準差從2.1%降至0.9%。該技術(shù)突破使得3nm制程的良率提升至92.5%,充分驗證了高壓電源技術(shù)創(chuàng)新對工藝均勻性的提升效果。

未來發(fā)展方向?qū)⒕劢褂谠訉涌涛g(ALE)級精密控制,通過開發(fā)亞微秒級脈沖序列與雙頻耦合技術(shù),實現(xiàn)單原子尺度的刻蝕均勻性控制。這需要高壓電源在保持20kV級輸出的同時,將電流控制精度提升至微安量級,推動半導體制造向埃米時代邁進。

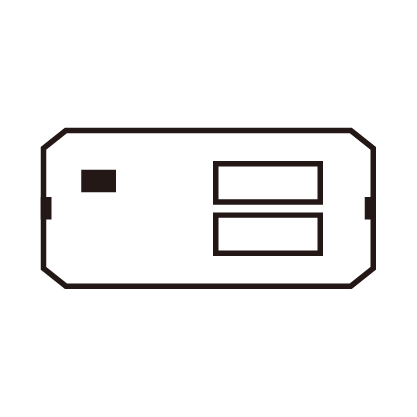

泰思曼 THP2345 系列高功率高壓電源,具有優(yōu)于峰峰值 0.1%的低紋波。內(nèi)部采用空氣絕緣方式,具備快速響應單元,具有精準的調(diào)節(jié)和極低的電弧放電電流。在諸如離子源等負阻性負載應用場合下,可高效可靠運行。

典型應用:耐壓測試;老化測試;刻蝕;鍍膜;半導體應用;離子源;加速器