鍍膜脈沖高壓電源的脈沖波形優(yōu)化

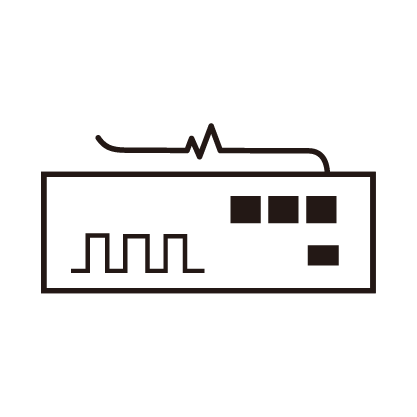

在鍍膜工藝領(lǐng)域,脈沖高壓電源的性能對(duì)鍍膜質(zhì)量起著決定性作用。而其中,脈沖波形的優(yōu)化成為提升鍍膜效果的關(guān)鍵環(huán)節(jié)。

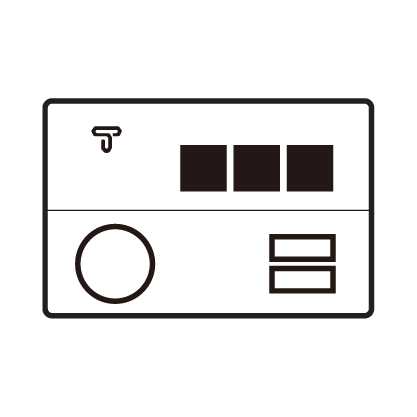

脈沖波形直接影響著鍍膜過程中的離子能量、離子轟擊頻率以及沉積速率等重要參數(shù)。不同的鍍膜材料和工藝要求,需要與之適配的特定脈沖波形。例如,在某些金屬鍍膜中,要求脈沖波形能夠提供高能量的離子束,以確保金屬原子能夠牢固地附著在基底表面,形成致密且附著力強(qiáng)的膜層。而對(duì)于一些有機(jī)鍍膜材料,過于強(qiáng)烈的離子轟擊可能會(huì)破壞有機(jī)物分子結(jié)構(gòu),此時(shí)則需要較為溫和、精確控制能量輸出的脈沖波形。

影響鍍膜脈沖高壓電源脈沖波形的因素眾多。電源內(nèi)部的電路拓?fù)浣Y(jié)構(gòu)是基礎(chǔ)因素之一。不同的電路設(shè)計(jì),如采用的開關(guān)元件類型、電感和電容的參數(shù)配置等,都會(huì)導(dǎo)致輸出脈沖波形的差異。例如,采用高速開關(guān)器件能夠?qū)崿F(xiàn)更快速的脈沖上升和下降沿,而合適的電感電容組合則可以對(duì)脈沖波形進(jìn)行整形,減少紋波。此外,負(fù)載特性也是不可忽視的因素。鍍膜過程中,隨著膜層的逐漸沉積,負(fù)載的電阻、電容等特性會(huì)發(fā)生變化,這反過來(lái)又會(huì)影響電源輸出的脈沖波形。如果電源不能及時(shí)適應(yīng)負(fù)載變化,脈沖波形就可能出現(xiàn)畸變,影響鍍膜質(zhì)量。

為實(shí)現(xiàn)鍍膜脈沖高壓電源脈沖波形的優(yōu)化,一系列技術(shù)手段被廣泛應(yīng)用。一方面,先進(jìn)的電路設(shè)計(jì)技術(shù)是核心。通過采用復(fù)雜的反饋控制電路,實(shí)時(shí)監(jiān)測(cè)輸出脈沖波形,并根據(jù)預(yù)設(shè)的理想波形進(jìn)行調(diào)整。例如,引入數(shù)字信號(hào)處理器(DSP)或現(xiàn)場(chǎng)可編程門陣列(FPGA),利用其強(qiáng)大的計(jì)算和邏輯控制能力,對(duì)電源的開關(guān)元件進(jìn)行精確控制,從而生成更接近理想形狀的脈沖波形。另一方面,采用智能算法對(duì)脈沖波形進(jìn)行優(yōu)化。如遺傳算法、粒子群優(yōu)化算法等,這些算法可以根據(jù)鍍膜工藝的實(shí)際需求,在眾多可能的波形參數(shù)組合中尋找最優(yōu)解,以實(shí)現(xiàn)最佳的鍍膜效果。同時(shí),對(duì)電源的電磁兼容性進(jìn)行優(yōu)化也十分重要。減少電源內(nèi)部及外部的電磁干擾,能夠避免干擾信號(hào)對(duì)脈沖波形的污染,保證波形的純凈度和穩(wěn)定性。

優(yōu)化后的脈沖波形在實(shí)際鍍膜生產(chǎn)中帶來(lái)了顯著的效益。在光學(xué)鍍膜領(lǐng)域,精確優(yōu)化的脈沖波形使得膜層的光學(xué)性能更加穩(wěn)定,反射率和透射率等指標(biāo)能夠更精準(zhǔn)地滿足設(shè)計(jì)要求,提升了光學(xué)鏡片等產(chǎn)品的質(zhì)量。在半導(dǎo)體芯片制造中的鍍膜工藝中,優(yōu)化的脈沖波形有助于形成均勻、高質(zhì)量的絕緣膜或?qū)щ娔ぃ岣咝酒牧计仿屎托阅堋?br />

總之,鍍膜脈沖高壓電源的脈沖波形優(yōu)化是一個(gè)綜合性的技術(shù)難題,涉及電路設(shè)計(jì)、負(fù)載匹配、算法優(yōu)化以及電磁兼容等多個(gè)方面。通過不斷探索和應(yīng)用新的技術(shù)手段,實(shí)現(xiàn)脈沖波形的精準(zhǔn)優(yōu)化,將為鍍膜工藝的發(fā)展注入強(qiáng)大動(dòng)力,推動(dòng)相關(guān)產(chǎn)業(yè)邁向更高水平。