鍍膜高壓電源的膜層致密性優(yōu)化

在材料表面處理領(lǐng)域,鍍膜技術(shù)憑借其能夠賦予材料特殊性能的優(yōu)勢(shì),被廣泛應(yīng)用于光學(xué)、電子、機(jī)械等眾多行業(yè)。而鍍膜高壓電源作為鍍膜工藝中的核心設(shè)備之一,對(duì)膜層質(zhì)量起著關(guān)鍵作用,其中膜層致密性更是衡量膜層質(zhì)量的重要指標(biāo)。優(yōu)化鍍膜高壓電源的相關(guān)參數(shù)與性能,對(duì)于提升膜層致密性意義重大。

鍍膜高壓電源為鍍膜過(guò)程提供必要的電場(chǎng)環(huán)境,離子在電場(chǎng)作用下加速撞擊靶材,使得靶材原子濺射出來(lái)并沉積在基底表面形成膜層。在此過(guò)程中,電源輸出電壓、電流的穩(wěn)定性以及波形特性等因素,均會(huì)對(duì)膜層致密性產(chǎn)生顯著影響。

輸出電壓是影響膜層致密性的關(guān)鍵參數(shù)之一。若電壓過(guò)低,離子獲得的能量不足,無(wú)法充分濺射靶材原子,導(dǎo)致膜層生長(zhǎng)速率緩慢,且原子沉積時(shí)缺乏足夠動(dòng)力緊密排列,從而降低膜層致密性。相反,過(guò)高的電壓會(huì)使離子能量過(guò)高,可能造成靶材過(guò)度濺射,產(chǎn)生大量高能粒子,這些粒子在基底表面沉積時(shí)易形成缺陷,同樣不利于膜層致密性的提升。因此,精準(zhǔn)調(diào)控高壓電源輸出電壓至合適范圍,是優(yōu)化膜層致密性的基礎(chǔ)。

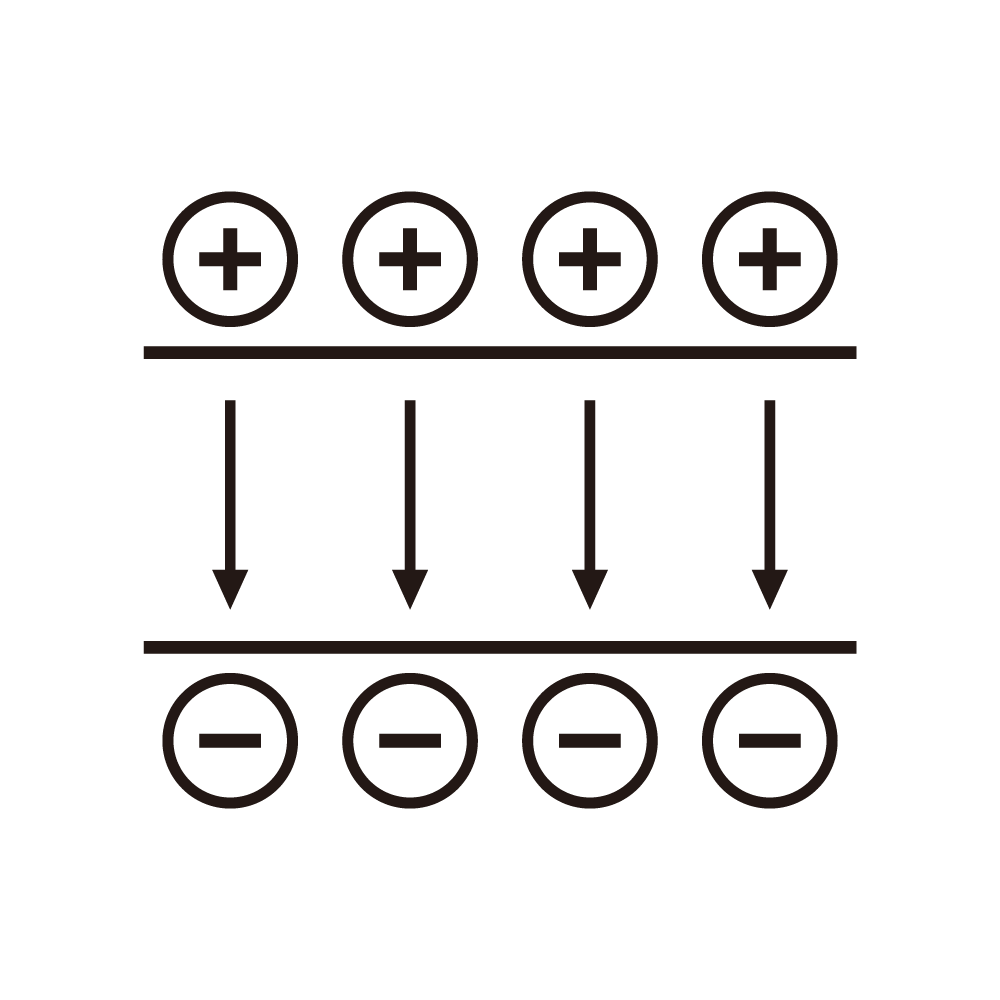

電源輸出電流的穩(wěn)定性也至關(guān)重要。電流波動(dòng)會(huì)導(dǎo)致濺射過(guò)程不穩(wěn)定,使得靶材原子濺射速率不均勻。當(dāng)濺射速率忽快忽慢時(shí),膜層在生長(zhǎng)過(guò)程中原子堆積的均勻性被破壞,容易出現(xiàn)空洞、縫隙等缺陷,嚴(yán)重影響膜層致密性。通過(guò)采用先進(jìn)的電流控制技術(shù),如閉環(huán)反饋控制,實(shí)時(shí)監(jiān)測(cè)并調(diào)整電流,確保其穩(wěn)定輸出,有助于改善膜層質(zhì)量,提高膜層致密性。

此外,高壓電源輸出波形的特性也不容忽視。不同的波形,如直流、脈沖等,對(duì)鍍膜過(guò)程和膜層致密性有不同影響。脈沖波形能夠在短時(shí)間內(nèi)提供高能量,促進(jìn)離子與靶材的有效作用,同時(shí)在脈沖間歇期,基底表面有足夠時(shí)間進(jìn)行原子的重排與調(diào)整,有利于形成更致密的膜層結(jié)構(gòu)。合理選擇和優(yōu)化電源輸出波形,可顯著提升膜層致密性。

為進(jìn)一步優(yōu)化膜層致密性,還可結(jié)合鍍膜工藝中的其他因素。例如,控制鍍膜過(guò)程中的真空度,合適的真空環(huán)境能減少雜質(zhì)氣體對(duì)膜層生長(zhǎng)的干擾,使原子沉積更加純凈、緊密。同時(shí),精確控制基底溫度,適當(dāng)?shù)臏囟扔兄谠釉诨妆砻娴倪w移和擴(kuò)散,促進(jìn)膜層原子的有序排列,提高膜層致密性。

綜上所述,通過(guò)對(duì)鍍膜高壓電源的輸出電壓、電流穩(wěn)定性以及波形特性等關(guān)鍵參數(shù)的優(yōu)化,同時(shí)協(xié)同控制鍍膜工藝中的真空度和基底溫度等因素,能夠有效提升膜層致密性,從而為各行業(yè)提供更高質(zhì)量的鍍膜產(chǎn)品,滿足日益增長(zhǎng)的材料性能需求。